Basic System Accelerator Integration Verification Soc Labs

Find inspiration for Basic System Accelerator Integration Verification Soc Labs with our image finder website, Basic System Accelerator Integration Verification Soc Labs is one of the most popular images and photo galleries in Stanford University Edge Ml Accelerator Soc Design Using Catapult Hls Gallery, Basic System Accelerator Integration Verification Soc Labs Picture are available in collection of high-quality images and discover endless ideas for your living spaces, You will be able to watch high quality photo galleries Basic System Accelerator Integration Verification Soc Labs.

aiartphotoz.com is free images/photos finder and fully automatic search engine, No Images files are hosted on our server, All links and images displayed on our site are automatically indexed by our crawlers, We only help to make it easier for visitors to find a free wallpaper, background Photos, Design Collection, Home Decor and Interior Design photos in some search engines. aiartphotoz.com is not responsible for third party website content. If this picture is your intelectual property (copyright infringement) or child pornography / immature images, please send email to aiophotoz[at]gmail.com for abuse. We will follow up your report/abuse within 24 hours.

Related Images of Basic System Accelerator Integration Verification Soc Labs

Stanford University Edge Ml Accelerator Soc Design Using Catapult Hls

Stanford University Edge Ml Accelerator Soc Design Using Catapult Hls

640×360

Stanford University Edge Ml Accelerator Soc Design Using Catapult Hls

Stanford University Edge Ml Accelerator Soc Design Using Catapult Hls

1719×1371

The Ai Accelerator Ecosystem For Custom Ml Design In Hls

The Ai Accelerator Ecosystem For Custom Ml Design In Hls

680×429

Hls For Machine Learning In Increasingly Complex Edge Ai Applications

Hls For Machine Learning In Increasingly Complex Edge Ai Applications

680×412

Aiml Accelerator Tutorial C Level Design And Verification Using Hls

Aiml Accelerator Tutorial C Level Design And Verification Using Hls

600×337

High Level Synthesis Drives Next Gen Edge Ai Accelerators Electronic

High Level Synthesis Drives Next Gen Edge Ai Accelerators Electronic

950×952

Demo Nvidias Use Of Catapult Hls For Building Ml Inference

Demo Nvidias Use Of Catapult Hls For Building Ml Inference

680×325

The Ai Accelerator Ecosystem For Custom Ml Design In Hls

The Ai Accelerator Ecosystem For Custom Ml Design In Hls

721×400

Hls Based Accelerator Design In Esp Download Scientific Diagram

Hls Based Accelerator Design In Esp Download Scientific Diagram

720×972

Effective Swhw Co Design Of Specialized Ml Accelerators With Catapult

Effective Swhw Co Design Of Specialized Ml Accelerators With Catapult

1525×830

Esp Tutorial How To Design An Accelerator In Cc Mentor Catapult

Esp Tutorial How To Design An Accelerator In Cc Mentor Catapult

512×195

Video 1 Catapult High Level Synthesis Hls 101 Youtube

Video 1 Catapult High Level Synthesis Hls 101 Youtube

1280×720

Ai Hardware Summit Report 2 Lowering Power At The Edge With Hls

Ai Hardware Summit Report 2 Lowering Power At The Edge With Hls

2048×1070

Early Design And Validation Of An Ai Accelerators Performance Using An

Early Design And Validation Of An Ai Accelerators Performance Using An

640×360

Cornell University Building Sparse Linear Algebra Accelerators With

Cornell University Building Sparse Linear Algebra Accelerators With

1200×627

Hls Enables The Next Generation Of Edge Ai Accelerators

Hls Enables The Next Generation Of Edge Ai Accelerators

768×382

Risc V And Soc Architectural Exploration For Ai And Ml Accelerators Ppt

Risc V And Soc Architectural Exploration For Ai And Ml Accelerators Ppt

1024×768

Jerome Bortolami On Linkedin Aiml Accelerator Tutorial C Level

Jerome Bortolami On Linkedin Aiml Accelerator Tutorial C Level

2394×1351

Hardware Accelerator Design For Machine Learning Intechopen

Hardware Accelerator Design For Machine Learning Intechopen

2691×2875

Aiml Accelerator Tutorial C Level Design And Verification Using Hls

Aiml Accelerator Tutorial C Level Design And Verification Using Hls

649×494

A Hardware Centric Approach To Checking Hls Code Before Synthesis Hls

A Hardware Centric Approach To Checking Hls Code Before Synthesis Hls

580×402

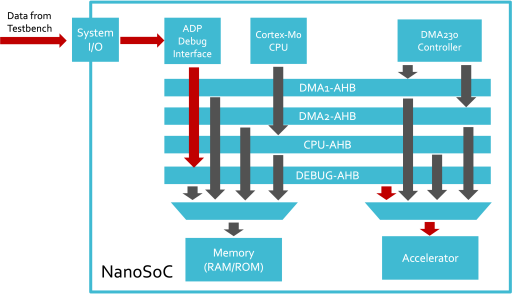

Basic System Accelerator Integration Verification Soc Labs

Basic System Accelerator Integration Verification Soc Labs

1368×725

Shows The Overall Accelerator Architecture Design Our Accelerator

Shows The Overall Accelerator Architecture Design Our Accelerator

600×350

Learning To Design Accurate Deep Learning Accelerators With Inaccurate

Learning To Design Accurate Deep Learning Accelerators With Inaccurate

638×479

Nvidia Design And Verification Of A Machine Learning Accelerator Soc

Nvidia Design And Verification Of A Machine Learning Accelerator Soc

640×640

Risc V And Soc Architectural Exploration For Ai And Ml Accelerators

Risc V And Soc Architectural Exploration For Ai And Ml Accelerators

Efficientnet Edgetpu Creating Accelerator Optimized Neural Networks

Efficientnet Edgetpu Creating Accelerator Optimized Neural Networks

Overview Of The Accelerator And Soc Design Flows With An Example Of Soc

Overview Of The Accelerator And Soc Design Flows With An Example Of Soc