Network On A Chip Expanding The Possibilities Of Integrated Circuits

Find inspiration for Network On A Chip Expanding The Possibilities Of Integrated Circuits with our image finder website, Network On A Chip Expanding The Possibilities Of Integrated Circuits is one of the most popular images and photo galleries in Pdf Bist For Network On Chip Communication Infrastructure Based On Gallery, Network On A Chip Expanding The Possibilities Of Integrated Circuits Picture are available in collection of high-quality images and discover endless ideas for your living spaces, You will be able to watch high quality photo galleries Network On A Chip Expanding The Possibilities Of Integrated Circuits.

aiartphotoz.com is free images/photos finder and fully automatic search engine, No Images files are hosted on our server, All links and images displayed on our site are automatically indexed by our crawlers, We only help to make it easier for visitors to find a free wallpaper, background Photos, Design Collection, Home Decor and Interior Design photos in some search engines. aiartphotoz.com is not responsible for third party website content. If this picture is your intelectual property (copyright infringement) or child pornography / immature images, please send email to aiophotoz[at]gmail.com for abuse. We will follow up your report/abuse within 24 hours.

Related Images of Network On A Chip Expanding The Possibilities Of Integrated Circuits

Pdf Bist For Network On Chip Communication Infrastructure Based On

Pdf Bist For Network On Chip Communication Infrastructure Based On

850×1202

Memory Bist Partitioning On A Typical System On Chip Download

Memory Bist Partitioning On A Typical System On Chip Download

850×519

On Chip Communication Evolution Download Scientific Diagram

On Chip Communication Evolution Download Scientific Diagram

850×441

Figure 1 From An On Chip Adc Bist Solution And The Bist Enabled

Figure 1 From An On Chip Adc Bist Solution And The Bist Enabled

670×622

Trustworthy System On Chip Design Using Secure On Chip Communication

Trustworthy System On Chip Design Using Secure On Chip Communication

1478×573

Figure 2 From Flexible Architectures For Ldpc Decoders Based On Network

Figure 2 From Flexible Architectures For Ldpc Decoders Based On Network

652×1184

A New Bist Based Test Approach With The Fault Location Capability For

A New Bist Based Test Approach With The Fault Location Capability For

850×1129

Ppt On Chip Communication Architecture And Design Powerpoint

Ppt On Chip Communication Architecture And Design Powerpoint

1024×768

Pdf A Comparison Of Network On Chip And Buses Semantic Scholar

Pdf A Comparison Of Network On Chip And Buses Semantic Scholar

514×498

Ppt Cmpe 511 On Chip Networks A Scalable Communication Centric

Ppt Cmpe 511 On Chip Networks A Scalable Communication Centric

1024×768

Memory Bist For Automotive Designs Tessent Solutions

Memory Bist For Automotive Designs Tessent Solutions

2071×1123

Ppt On Chip Communication Networks On Chip Nocs Powerpoint

Ppt On Chip Communication Networks On Chip Nocs Powerpoint

1024×768

Ppt Networks On Chip A Very Quick Introduction Powerpoint

Ppt Networks On Chip A Very Quick Introduction Powerpoint

1024×768

Electronics Free Full Text Q Function Based Traffic And Thermal

Electronics Free Full Text Q Function Based Traffic And Thermal

2609×1546

Network On Chip Topologies Potentials Technical Challenges Recent

Network On Chip Topologies Potentials Technical Challenges Recent

708×170

Test Data Flow While The Sb Test And Sbtro Instructions Are Executed

Test Data Flow While The Sb Test And Sbtro Instructions Are Executed

742×943

Figure 1 From Low Area Boundary Bist Architecture For Mesh Like Network

Figure 1 From Low Area Boundary Bist Architecture For Mesh Like Network

592×534

Ppt An Introduction To Built In Self Test Bist Powerpoint

Ppt An Introduction To Built In Self Test Bist Powerpoint

1023×708

Pdf Non Blocking Bist For Continuous Reliability Monitoring Of

Pdf Non Blocking Bist For Continuous Reliability Monitoring Of

850×1100

Pdf Bist For Network On Chip Interconnect Infrastructures

Pdf Bist For Network On Chip Interconnect Infrastructures

850×1100

The Network On Chip Interconnect Is The Soc Edn

The Network On Chip Interconnect Is The Soc Edn

2814×1311

Figure 1 From Non Blocking Bist For Continuous Reliability Monitoring

Figure 1 From Non Blocking Bist For Continuous Reliability Monitoring

542×270

On Chip Communication Architectures System On Chip Interconnect

On Chip Communication Architectures System On Chip Interconnect

500×500

Figure 3 From An On Chip Adc Bist Solution And The Bist Enabled

Figure 3 From An On Chip Adc Bist Solution And The Bist Enabled

602×548

Network On Chip Architecture Displaces A Crossbar Approach Edn Asia

Network On Chip Architecture Displaces A Crossbar Approach Edn Asia

2633×2091

Micromachines Free Full Text Optimal Method For Test And Repair

Micromachines Free Full Text Optimal Method For Test And Repair

3000×1968

Ppt Networks On Chip A Very Quick Introduction Powerpoint

Ppt Networks On Chip A Very Quick Introduction Powerpoint

1024×768

On Chip Communication Network For Efficient Training Of Deep

On Chip Communication Network For Efficient Training Of Deep

624×436

Figure 2 From An On Chip Adc Bist Solution And The Bist Enabled

Figure 2 From An On Chip Adc Bist Solution And The Bist Enabled

850×1100

Pdf Test Scheduling For Network On Chip With Bist And Precedence

Pdf Test Scheduling For Network On Chip With Bist And Precedence

1024×768

Ppt Design Synthesis And Test Of Network On Chips Powerpoint

Ppt Design Synthesis And Test Of Network On Chips Powerpoint

474×668

Figure 4 From Adaptation Of Standard Rt Level Bist Architectures For

Figure 4 From Adaptation Of Standard Rt Level Bist Architectures For

1026×622

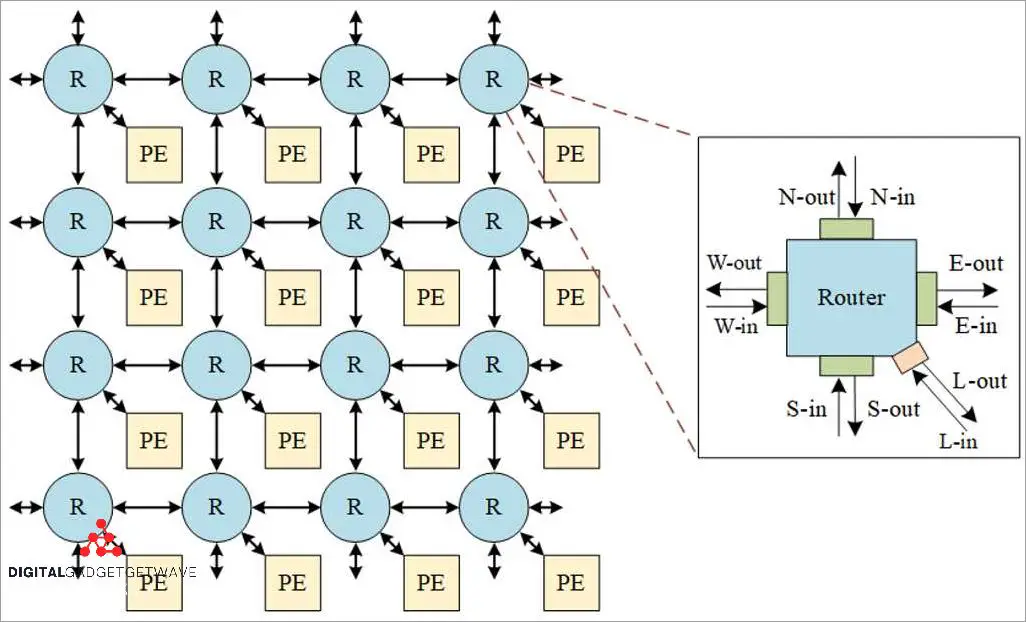

Network On A Chip Expanding The Possibilities Of Integrated Circuits

Network On A Chip Expanding The Possibilities Of Integrated Circuits